什么是干法刻蚀的凹槽效应?

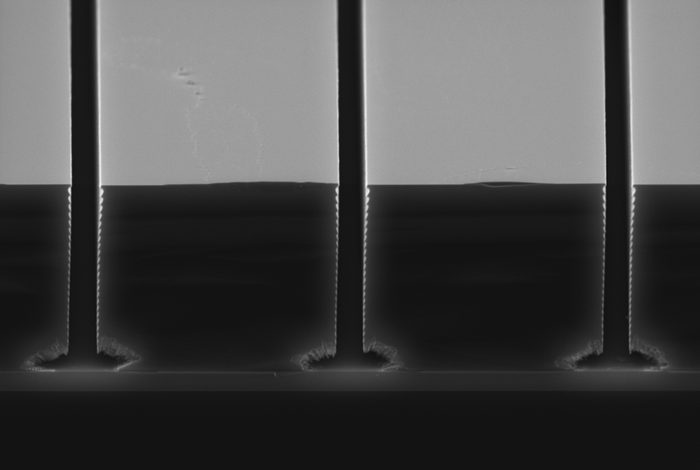

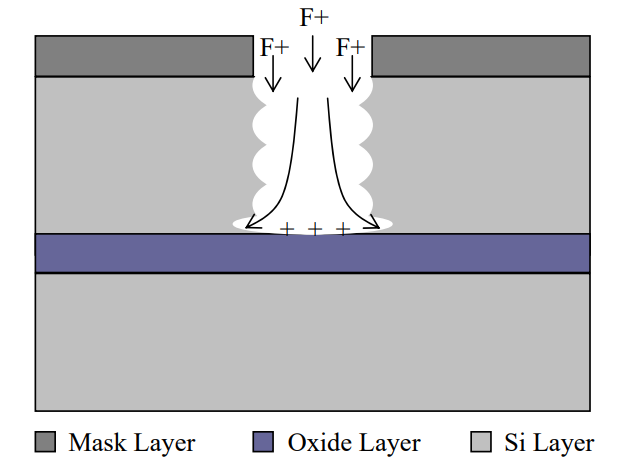

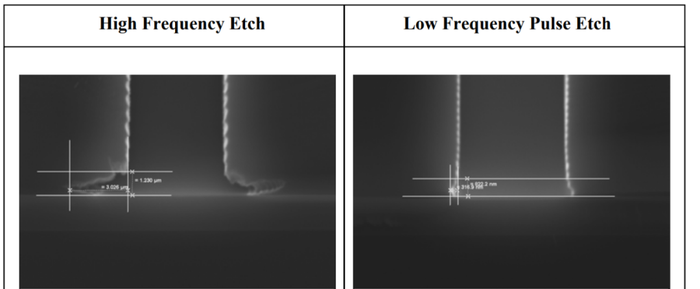

在刻蚀SOI衬底时,通常会发生一种凹槽效应,导致刻蚀的形貌与预想的有很大出入。那么什么是凹槽效应?什么原因引起的?怎么抑制这种异常效应呢?

什么是凹槽效应?

分步刻蚀适合优化在单一参数设置下可能出现的问题,有利于解决复杂结构中的刻蚀问题。

Tom聊芯片智造

展源

何发

相关文章

-

AAS法分析茶叶中的铅,镉,砷

2020-05-27

-

检测有机氯类农药,气相色谱法检测法

2021-01-12

-

QC, IQC, IPQC, QA,到底是什么鬼?

2020-05-27

-

铜互连为什么不用干法刻蚀的方法?

2023-11-22

-

等离子体刻蚀

2020-05-27

-

离子束刻蚀

2020-05-27

-

-

HILIC法优化分离效果

2020-05-27

-

红外光谱分析,你了解多少?

2021-01-11

加载更多